LVDS定义

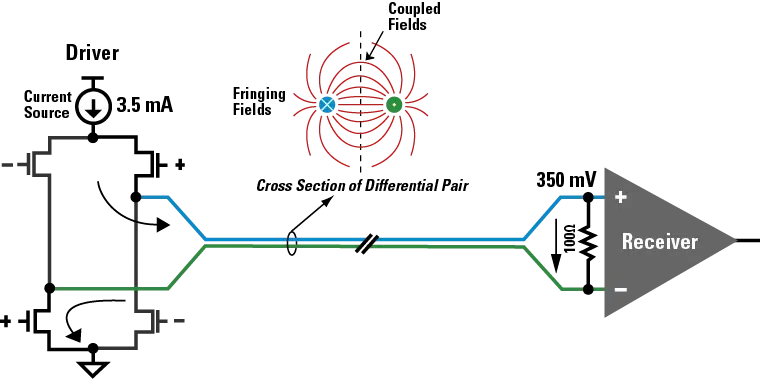

LVDS(Low-Voltage Differential Signaling,低电压差分信号)是一种用于高速数据传输的电气标准。它利用差分信号的方式来提高传输速率和信号完整性,同时降低功耗和干扰。它是一种电气传输系统,可以在成本低廉的双绞线铜电缆上以极高的速度运行。这些双绞线能维持 LVDS 数据信号所需的 100 欧姆差分阻抗。LVDS 因其在提供高数据速率的同时消耗更少的功率,成为差分信号传输的首选标准。它采用高速模拟电路技术,通过铜互连实现每秒数 Gb 的数据传输,广泛应用于高速数据传输领域。这些特点使 LVDS 成为业界最流行的差分数据传输标准。

Lvds电缆

LVDS 电缆是低功耗、高数据传输的理想选择,广泛应用于计算机系统。在引入 LVDS 电缆之前,数据传输速率较低且电缆占用较多空间。SCSI 标准现已支持 LVDS,使电缆组件能够实现更高的数据速率和更长的电缆长度。

LVDS 电缆组件也用于视频接口设备,特别是在将视频数据从图形适配器传输到计算机显示器时,如 LCD 屏幕、FPD-Link 或 OpenLDI 标准。LVDS 电缆组件支持的最大像素时钟为 112 MHz,这使得在 60 Hz 刷新率下可实现 1400 x 1050(SXGA+)的显示分辨率。双链路配置下,在 60 Hz 刷新率下,显示分辨率可提高到 2048 x 1536(QXGA)。FPD-Link 电缆长度可达约 5 米,而 LDI 标准的电缆长度可扩展到约 10 米。使用的典型电缆是大约 28 – 32 AWG 的双绞线,但是,FCC / FPC 电缆非常常见,尤其是在与笔记本电脑等设备或空间宝贵的设备一起使用时。

Lvds 接口

LVDS 接口是一种高速、低功耗且抗噪声的数字接口,通过差分信号对实现可靠、快速的数据传输。其电气特性,如低电压电平、高差分阻抗和出色的共模抑制,确保了在长距离传输中的信号完整性。

常见的 LVDS 接口变体包括:

Multidrop LVDS:适用于多个接收器共享一个发射器的场景。

Multipoint LVDS:设计用于公共总线上的多个发射器和接收器之间的双向通信。

Lvds信号

LVDS 信号(Low-Voltage Differential Signaling Signal,低压差分信号)是一种用于高速数据传输的电气信号类型。它通过差分信号对传输数据,以提高传输速率、降低功耗并增强抗干扰能力。

差分信号对:LVDS 信号通过一对互补的电信号线传输数据。每对线路分别传送正向和负向信号,接收端通过比较这两条信号线的电压差来解码信息。这种差分传输方式能够有效抵抗噪声和干扰。

低电压操作:LVDS 信号通常在低电压下工作,例如 1.2V,这有助于降低功耗和发热。

高数据传输速率:LVDS 支持高速数据传输,通常在几 Gb/s 的范围内,适合需要高带宽的应用。

高差分阻抗:LVDS 信号线的阻抗为 100 欧姆,这有助于减少信号反射和衰减,保持信号的完整性。

共模抑制:LVDS 信号具有出色的共模抑制能力,能够有效抑制共模噪声,进一步增强数据传输的稳定性。

Lvds 电压电平

差分电压(Vdiff):LVDS 的差分电压是指正向信号和负向信号之间的电压差。LVDS 标准通常要求差分电压在 0.1V 至 0.6V 范围内。具体的电压值可能会根据不同的实现和设备要求有所不同。

典型的差分电压范围是 0.2V 到 0.4V。

单端电压(VCM):LVDS 信号线上的单端电压指的是每条线相对于地的电压。LVDS 标准通常工作在低电压环境下,典型的单端电压为 0V 到 1.2V。

对于 LVDS 信号,通常有一个公共模电压(VCM),它可能是 1.2V 的参考电压,但在实际应用中,电压可能会有所调整。

信号电平的具体例子:

逻辑高电平:在一个典型的 LVDS 实现中,当差分对中的正信号线电压高于负信号线时,通常表示逻辑高电平。

逻辑低电平:当差分对中的正信号线电压低于负信号线时,通常表示逻辑低电平。

咨询信息和购买欢迎联系我们:caichips.com